3/29 월 ~ 4/4 일 : 4시간 15분

3/29 월 : 2시간

3/30 화 : 2시간 15분

시작 385 - 396

3/29 월 : 2시간

385 - 390

5.2. 메모리 기술

오늘날 메모리 계층구조에서는 네 가지 주요 기술이 사용된다.

1. SRAM(static random access memory) - 캐시(cache)

2. DRAM(dynamic random access memory) - 메인 메모리(main memory)

DRAM은 SRAM보다 훨씬 느리지만 비트당 가격이 덜 비싸다.

3. 플래시 메모리

4. 자기 디스크

이 절의 남은 부분에서 각 메모리 기술을 설명한다.

SRAM 기술

1. 단순한 집적회로로서, 읽기나 쓰기를 제공하는 접근 포트가(일반적으로) 하나 있는 메모리 배열이다.

2. 읽기 접근 시간과 쓰기 접근 시간이 다를 수는 있지만, 어떤 데이터든지 접근 시간은 같다.

3. 리프레시가 필요 없으므로 접근 시간은 사이클 시간과 거의 같다.

4. 읽을 때 정보가 바뀌지 않게 하기 위하여 비트당 6개 내지 8개의 트랜지스터를 사용한다.

5. 대기 모드에서 데이터 값을 유지하기 위해 최소한의 전력만을 사용한다.

DRAM 기술

1. SRAM에서는 전력이 공급되는 한 그 값이 무한히 유지된다.

2. DRAM에서는 셀에 기억되는 값이 전하로 커패시터에 저장된다.

3. 저장된 값을 읽거나 새로 쓰기 위하여 저장된 전하에 접근하는 데 트랜지스터를 하나 사용한다.

4. 저장된 비트 하나 당 트랜지스터 하나만 사용하므로 SRAM에 비하여 훨씬 더 집적도가 높고 값도 싸다.

5. 커패시터에 전하를 저장하기 때문에 무한히 저장될 수 없으므로 주기적으로 리프레시가 필요하다.

6. 그러므로 SRAM 셀에서 정적 저장이라고 하는 것에 반해, 이런 메모리 구조를 동적이라고 부른다.

셀을 리프레시하기 위해서는 단순히 저장된 값을 읽고 다시 쓴다.

전하는 수 밀리초 동안 유지될 수 있다.

모든 비트를 하나씩 DRAM에서 읽어서 다시 쓴다면,

계속 DRAM을 리프레시해야 하므로 기억된 값에 접근할 시간이 없게 된다.

다행히도 DRAM은 두 단계 디코딩 구조를 갖는다.

이 구조는 읽기 사이클에서 전체 행(워드라인을 공유하는)을 한꺼번에 읽은 후 바로 쓰기를 하여,

한 행을 통째로 리프레시할 수 있도록 해준다.

리프레시에 도움이 되는 행 구조는 성능 향상에도 도움이 된다.

성능을 향상시키기 위하여 DRAM은 행을 버퍼링해서 반복적으로 접근한다.

버퍼는 SRAM처럼 동작한다.

다음 행에 접근할 때까지는 주소 값만 바꾸면 버퍼 내의 아무 비트에나 접근할 수 있다.

이 기능은 같은 행 내의 비트 접근 시간을 훨씬 줄여 주므로 접근 시간을 크게 개선한다.

칩을 더 크게 만들면 칩의 메모리 대역폭 또한 커지게 된다.

어떤 행이 버퍼에 있으면, DRAM의 대역폭(일반적으로 4, 8, 또는 16비트)이 얼마든지 간에 연속된 주소를 사용해서 또는 버퍼 내 시작 주소와 블록 전송을 이용해서 전송할 수 있다. ← 뭔소리야

프로세서와의 인터페이스를 더욱 향상시키기 위해 DRAM은 클럭을 추가할 수 있는데

이것을 동기화 DRAM 또는 SDRAM이라 부른다.

SDRAM의 장점은 클럭을 사용하므로 메모리와 프로세서를 동기화하는 시간이 필요 없다는 것이다.

동기화 DRAM의 속도가 빠른 이유는 추가 주소지정 대신 클럭이 연속적인 비트들을 버스트 모드로 전송할 수 있게 하기 때문이다.

가장 빠른 버전은 DDR(double data rate) SDRAM이라고 불린다.

이 이름은 클럭의 상승 에지와 하강 에지 각각에서 데이터가 전송되는 것을 의미한다.

클럭과 데이터 전송 폭으로부터 기대할 수 있듯이 2배의 대역폭을 가능하게 한다.

이 중 최신 버전은 DDR4라고 불린다.

DDR4-3200 DRAM은 초당 32억(3200x10^6)번의 전송이 가능하며, 1600MHz 클럭을 사용한다.

이와 같이 큰 대역폭을 유지하기 위해서는 DRAM 내부에 좋은 구조가 필요하다.

단순하게 더 빠른 행 버퍼를 사용하는 대신에, DRAM은 내부적으로 여러 뱅크에서 읽기와 쓰기가 가능하도록 구성되었다.

각각의 뱅크는 자신의 행 버퍼를 가지고 있다.

여러 뱅크에 주소를 보낼 수 있게 하여 동시에 읽고 쓰기가 가능하게 하였다.

예를 들어 뱅크가 4개일 때, 한 번의 접근 시간으로 4배의 대역폭을 제공하기 위해 4개의 뱅크에 돌아가면서 접근하다.

이 순환 접근 방식은 주소 인터리빙(address interleaving)이라고 한다.

플래시 메모리

전기적으로 지울 수 있고 프로그래밍이 가능한 ROM(EEPROM)의 한 종류이다.

디스크나 DRAM과는 달리 플래시 메모리의 쓰기는 비트를 마모시킨다.

이 단점을 극복하기 위하여 대부분의 플래시 제품은 여러 번 쓰기가 수행된 블록을 덜 사용된 블록에 remapping해서 쓰기를 분산시키는 제어기를 사용한다.

이 기법을 마모 균등화(wear leveling)라고 부른다.

마모 균등화를 사용하기 때문에 개인용 이동 단말기의 플래시가 잠재적 쓰기 한계를 넘는 경우는 거의 없다.

마모 균등화가 플래시의 잠재적 성능을 떨어뜨리지만,

상위 계층 소프트웨어가 각 블록의 마모를 관리하지 않는 한 사용할 수밖에 없다.

디스크 메모리

그림 5.6에서 볼 수 있듯이, 하드디스크는 원판의 집합으로 구성되어 있고

원판은 분당 5,400~15,000번의 속도로 회전한다.

금속 원판의 양측 면은 카세트나 비디오테이프와 같이 자성체로 코팅되어 있다.

하드디스크상의 정보를 읽거나 쓰기 위해서는 읽기/쓰기 헤드라고 불리는 작은 전자기 코일을 갖고 있는 움직이는 암(arm)이 필요하다.

각 디스크 표면은 트랙(track)이라고 불리는 동심원으로 나누어진다.

일반적으로 표면당 수만 개의 트랙이 존재한다.

각 트랙은 다시 정보를 담는 섹터(sector)로 나누어진다.

한 트랙의 수천 개의 섹터로 구성된다.

섹터는 일반적으로 512바이트에서 4096바이트까지의 크기를 갖는다.

자성 매체에는 섹터 번호, 공백 에러 정정 코드를 포함하는 섹터의 정보, 공백, 다음 번 섹터의 번호와 같은 순서로 기록된다.

각 면의 디스크 헤드는 서로 연결되어 있어서 함께 움직인다.

그러므로 모든 헤드는 각 면의 같은 트랙에 위치한다.

모든 면의 한 점에 위치한 헤드 아래에 놓인 모든 트랙은 실린더(cylinder)라고 부른다.

데이터에 접근하려면 운영체제가 세 단계에 걸친 명령어를 디스크에 내려야 한다.

1

적절한 트랙 위에 디스크 암을 갖다 놓는 일이다.

이 작업은 보통 탐색(seek)이라고 부르며

디스크 헤드를 원하는 트랙까지 이동시키는 데 걸리는 시간은 탐색 시간(seek time)이라고 한다.

2

헤드가 원하는 트랙에 도달하면 읽기/쓰기 헤드의 아래에 원하는 섹터가 위치할 때까지 기다려야만 한다.

이 시간을 회전 지연 시간(rotational latency 또는 rotational delay)이라고 부른다.

3

디스크 접근의 마지막 요소는 블록 하나를 전송하는 시간, 즉 전송 시간(transfer time)이다.

전송 시간은 섹터의 크기, 회전 속도, 트랙의 저장 밀도의 함수이다.

자기 디스크와 반도체 메모리 기술 사이의 두 가지 큰 차이점은

디스크는 기계 장치이므로 접근 시간이 길고(플래시는 1000배 정도 빠르고 DRAM은 100,000배 정도 빠르다.)

디스크는 적당한 가격에 아주 높은 저장 용량을 갖기 때문에 훨씬 싸다는 점(10~100배 정도 싸다)이다.

3/30 화 : 2시간 15분

390 - 396

5.3 캐시의 기본

도서관의 예에서,책상은 캐시(조사를 해야 하는 것(책)들을 저장한 안전한 장소)의 기능을 수행하였다.

캐시(cache)는 이 계층을 갖춘 최초의 상용 컴퓨터에서 메인 메모리와 프로세서 사이에 있는 메모리 계층을 나타내기 위해 선택된 이름이다.

4장 데이터패스의 메모리들은 간단히 캐시로 대체될 수 있다.

오늘날에도 이렇게 많이 사용되고 있는 단어이지만, 접근의 지역성을 이용하는 모든 기억장치를 이렇게 부를 수 있다.

이 절에서는 프로세서가 한 순간에 필요로 하는 데이터는 한 워드이고,

블록 또한 한 워드로만 이루어진 아주 단순한 캐시를 먼저 살펴본다.

그림 5.7은 캐시에 없는 데이터를 요청하기 전과 후의 캐시 상태를 보여 준다.

요청하기 전의 캐시에는 최근에 접근한 X1, X2, .... , Xn-1이 존재하고, 프로세서는 캐시에 없는 워드 Xn을 요청하였다.

이 요구는 실패를 발생시키고 워드 Xn을 메모리로부터 캐시로 가져오게 된다.

캐시 내에 특정 데이터의 존재 여부 확인 → 메모리 주소에 기반을 두고 할당 → 위치 고정

그림 5.7의 시나리오를 살펴보면, 우리가 해결해야 할 두 가지 의문이 생기게 된다.

즉 데이터가 캐시 내에 있는지 어떻게 알 수 있는가? 그리고 알 수 있다면 어떻게 찾을 수 있는가?

각 워드가 캐시 내의 딱 한 장소에만 있을 수 있다면 워드가 캐시 내에 있는지 없는지를 바로 알 수 있다.

메모리의 각 워드에 캐시 내의 위치를 할당하는 가장 간단한 방법은 메모리 주소에 기반을 두고 할당하는 것이다.

이 캐시 구조를 직접 사상(direct mapped) 라고 한다.

왜냐하면 각 메모리 위치는 캐시 내의 딱 한 장소에 직접 사상되기 때문이다.

직접 사상 캐시가 사용하는 사상방식은 비교적 단순하다.

예를 들어 거의 모든 직접 사상 캐시는 블록을 찾기 위하여 다음의 사상 방식을 사용한다.

(블록 주소) modulo (캐시 내에 존재하는 전체 캐시 블록 수)

만약 캐시 내부의 전체 블록 수가 2의 자수승이면 modulo 연산은

간단히 주소의 하위 log2(캐시 내의 전체 블록 수) 비트만을 취하는 것으로 쉽게 계산할 수 있다.

따라서 8-블록 캐시는 블록 주소로 하위 3비트(8=2^3)를 사용한다.

예를 들어 그림 5.8은 8개의 워드로 된 직접 사상 캐시와

캐시 내의 위치 001과 101로 사상되는 메모리 주소 00001과 11101사이의 메모리 주소들을 보여 준다.

각 캐시의 엔트리는 여러 주소의 메모리 내용을 적재할 수 있다.

이때 캐시 내의 워드가 프로세서가 요구하는 것과 일치하는지를 어떻게 알 수 있을까?

캐시에 태그(tag)를 추가함으로써 이 문제를 해결할 수 있다.

태그는 캐시 내의 워드가 요청한 것인지 아닌지를 식별하는 데 필요한 주소 정보를 포함한다.

태그는 캐시의 인덱스로 사용되지 않은 주소의 윗부분 비트로 구성된다.

예를 들어 그림 5.8에서는 주소 비트 하위 3비트 인덱스 필드가 블록을 선택하는 데 사용되었으므로,

태그는 5비트의 주소 비트 중 상위 2비트가 된다.

또한 캐시 블록이 유효한 정보를 가지고 있는지를 알아내는 방법이 필요하다.

예를 들어 프로세서가 맨 처음 작업을 시작하면 캐시는 비어 있을 것이며, 태그 필드는 의미가 없을 것이다.

많은 명령어를 수행한 이후에도 캐시 엔트리 일부는 그림 5.7에서와 같이 비어있을 수 있다.

따라서 이들 엔트리를 위한 태그들은 무시되어야 한다는 것을 알 수 있다.

가장 많이 쓰이는 방법은 엔트리가 타당한 주소를 포함하는지를 표시하기 위해 유효 비트(vaild bit)를 캐시에 첨가하는 것이다.

이 비트가 1로 설정되어 있지 않으면, 이 엔트리에는 유효한 블록이 없는 것으로 간주한다.

이 절의 나머지 부분에서는 캐시에서 읽기가 어떻게 수행되는지와 읽기를 수행하기 위해 캐시가 어떻게 동작하는지에 초점을 맞추었다.

일반적으로 읽기처리는 캐시의 내용을 변화시키지 않기 때문에 쓰기 처리보다 조금 더 간단하다.

읽기가 어떻게 처리되고 캐시 실패가 어떻게 처리되는지에 대하여 살펴본 뒤,

실제 컴퓨터에서 구현된 캐시 구조와 캐시 쓰기 동작에 관해 알아본다.

캐시는 예측기법을 사용하는 가장 중요한 예라고 할 수 있다.

지역성의 원칙을 이용해서 메모리 상위 계층에서 필요한 데이터를 찾는다.

상위 계층에서 예측이 틀렸을 경우에는 하위 계층에서 적합한 데이터를 찾을 수 있는 기법을 제공한다.

현대 컴퓨터의 캐시 예측 적중률은 95% 이상이다.

캐시 접근

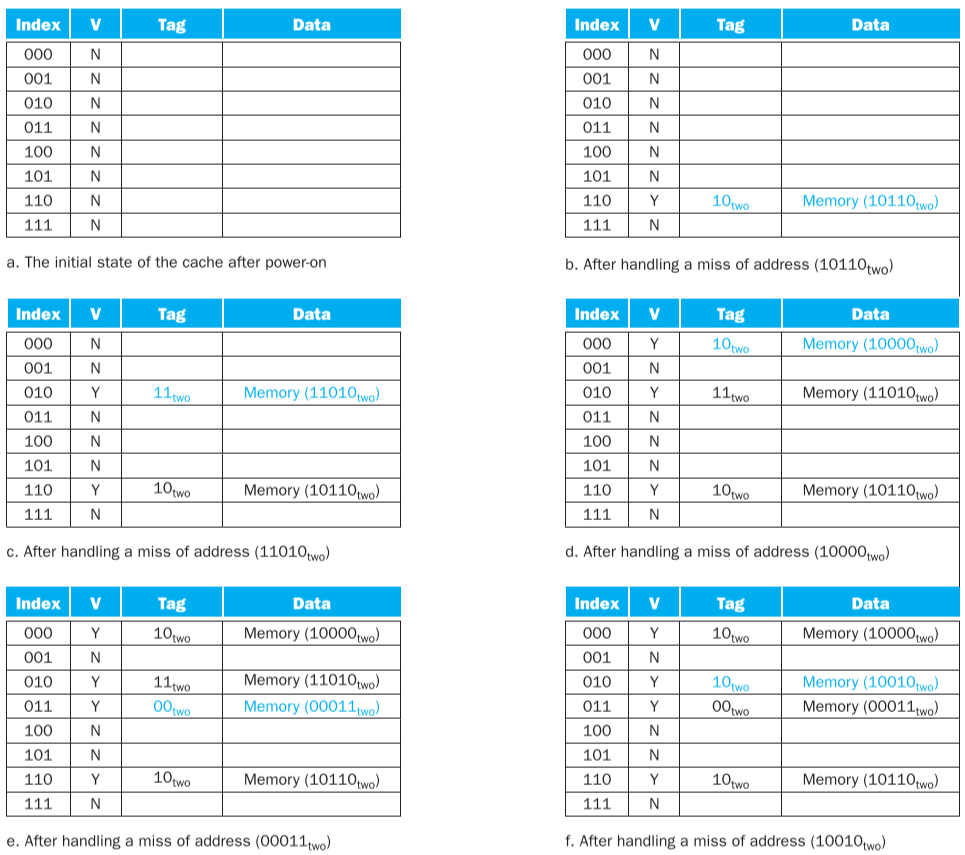

아래의 표는 캐시가 8개의 블록을 가지고 있고 모두 비어 있을 때, 아홉 번의 메모리 참조에 따른 동작을 보여 주고 있다.

그림 5.9는 캐시의 내용이 각 캐시 실패에 따라 어떻게 변경되는지를 보여 준다.

캐시 내에 8개의 블록이 있기 때문에 주소의 하위 3비트가 블록의 번호를 나타낸다.

캐시가 비어 있기 때문에 몇 개의 첫 번째 참조는 캐시 실패이다.

(그림 5.9는 각 메모리 참조의 동작을 설명하고 있다. )

여덟 번째 참조에서 블록에 대한 충돌이 생긴다.

캐시 블록 2(010)에 있던 주소 26(11010)의 워드는 주소 18(10010)로 교체된다.

이러한 상황은 캐시가 시간적 지역성을 활용할 수 있도록 해 준다.

즉, 최근에 접근된 워드는 더 이전에 접근된 워드를 교체한다.

이는 서가로부터 새로운 책이 필요하고 책상에 더 이상 빈 공간이 없을 때와 동일하다.

이미 책상에 있는 어떤 책을 서가로 되돌려 놓아야만 한다.

직접 사상 캐시에서는 새로 요청된 데이터가 들어갈 장소가 한 곳밖에 없기 때문에 교체시킬 선택안이 오직 하나다.

우리는 모든 주소에 대해 캐시 내의 어느 곳을 찾아야 할지 알 수 있다.

주소의 하위 비트들은 주소가 사상되는 유일한 캐시 엔트리를 찾는 데 사용할 수 있다.

그림 5.10은 참조된 주소가 어떻게 다음과 같이 나누어지는지를 보여 준다.

■ 캐시의 태그 필드 값과 비교하는 데 사용하는 태그 필드

■ 블록을 고르는 데 쓰이는 캐시 인덱스

캐시 블록의 인덱스는 그 블록의 태그 값과 함께 캐시 블록에 있는 워드의 실제 메모리 주소를 유일하게 표시할 수 있다.

MIPS 구조에서는 모든 주소가 4바이트로 정렬되어 4의 배수이기 때문에 모든 주소의 맨 오른쪽 2비트는 워드 내부의 바이트를 나타낸다.

따라서 최하위 두 비트는 블록 내의 워드를 선택할 때 이용되지 않는다.

캐시 구현에 필요한 총 비트 수는 캐시의 크기와 주소의 크기에 따라 결정된다.

왜냐하면 캐시는 데이터뿐만 아니라 태그를 위한 장소를 필요로 하기 때문이다.

위에서 블록의 크기는 한 워드이었지만 일반적으로는 여러 개의 워드가 된다. 아래와 같은 가정에서

■ 32비트의 주소

■ 직접 사상 캐시

■ 캐시는 2^n개의 블록을 가지고 있고 n개의 비트는 인덱스를 위하여 사용된다.

■ 캐시 블록의 크기는 2^m개 워드(2^m+2 개 바이트)이다. m개 비트는 블록 내부에서 워드 구별에 쓰이며, 두 비트는 주소 중 바이트 구별용으로 쓰인다.

태그 필드의 크기는

32 - (n + m + 2)

이다. 그리고 직접 사상 캐시의 전체 비트 수는

2^n X (블록 크기 + 태그 크기 + 유효 비트 크기)

이다. 블록의 크기는 2^m 개 워드(2^m+5개 비트)이고,

유효 필드를 위해 한 비트가 필요하므로 이 캐시의 전체 비트 수는

2^n X (2^m X 32 + (32 - n - m -2) + 1) = 2^n X (2^m X 32 + 31 - n - m)

이다. 하지만 일반적으로 캐시 크기는 유효 비트와 태크 필드의 크기는 제외하고 데이터 크기만 따진다.

따라서 그림 5.10의 캐시는 4KiB 캐시라고 부른다.